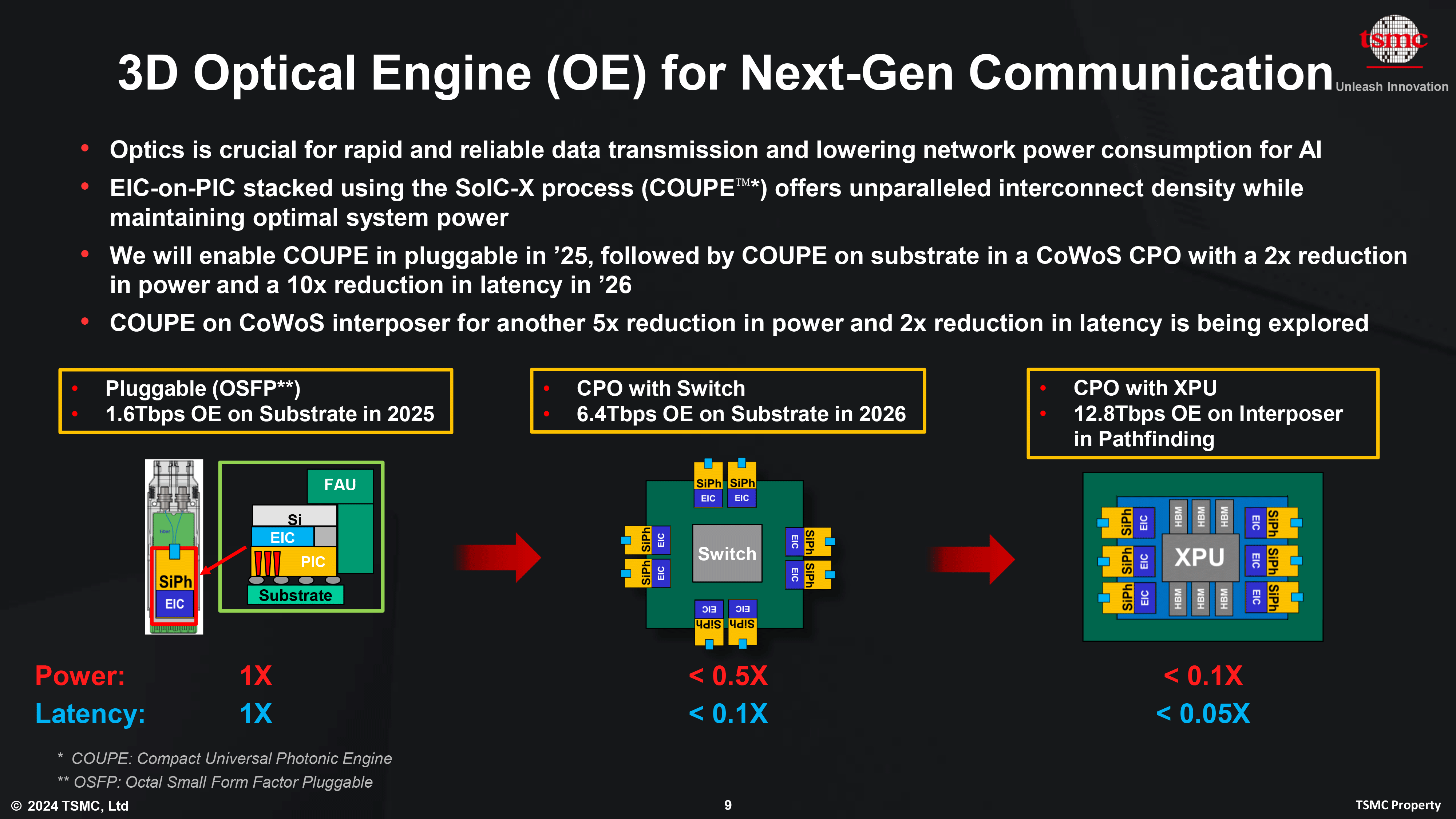

Se espera que la conectividad óptica (y especialmente la fotónica de silicio) se convierta en una tecnología crucial para permitir la conectividad de los centros de datos de próxima generación, en particular aquellos diseñados para aplicaciones HPC. Con los requisitos de ancho de banda cada vez mayores necesarios para mantenerse al día (y seguir ampliando) el rendimiento del sistema, la señalización de cobre por sí sola no será suficiente para mantenerse al día. Con ese fin, varias empresas están desarrollando soluciones de fotónica de silicio, incluidos proveedores fabulosos como TSMC, que esta semana describió su hoja de ruta para motores ópticos 3D como parte de su Simposio de Tecnología de América del Norte de 2024, y expuso su plan para llevar conectividad óptica de hasta 12,8 Tbps a Procesadores fabricados por TSMC.

El motor fotónico universal compacto (COUPE) de TSMC apila un circuito integrado electrónico en un circuito integrado fotónico (EIC-on-PIC) utilizando la tecnología de empaquetado SoIC-X de la empresa. La fundición afirma que el uso de su SoIC-X permite la impedancia más baja en la interfaz entre matrices y, por lo tanto, la mayor eficiencia energética. El propio EIC se produce con una tecnología de proceso de clase 65 nm.

El motor óptico 3D de primera generación (o COUPE) de TSMC se integrará en un dispositivo enchufable OSFP que funcionará a 1,6 Tbps. Se trata de una tasa de transferencia muy superior a los estándares actuales de Ethernet de cobre, que alcanzan un máximo de 800 Gbps, lo que subraya la ventaja inmediata del ancho de banda de las interconexiones ópticas para clústeres de computación fuertemente interconectados, sin importar los ahorros de energía esperados.

De cara al futuro, la segunda generación de COUPE está diseñada para integrarse en el paquete CoWoS como óptica empaquetada junto con un conmutador, lo que permite llevar las interconexiones ópticas al nivel de la placa base. Esta versión COUPE admitirá velocidades de transferencia de datos de hasta 6,40 Tbps con latencia reducida en comparación con la primera versión.

Se proyecta que la tercera versión de COUPE de TSMC (COUPE que se ejecuta en un interposer CoWoS) mejorará las cosas un paso más, aumentando las tasas de transferencia a 12,8 Tbps y acercando aún más la conectividad óptica al propio procesador. En la actualidad, COUPE-on-CoWoS se encuentra en la etapa de desarrollo y TSMC no tiene una fecha objetivo establecida.

En última instancia, a diferencia de muchos de sus pares de la industria, TSMC no ha participado en el mercado de la fotónica de silicio hasta ahora, dejándolo en manos de actores como GlobalFoundries. Pero con su estrategia de motor óptico 3D, la empresa entrará en este importante mercado mientras busca recuperar el tiempo perdido.