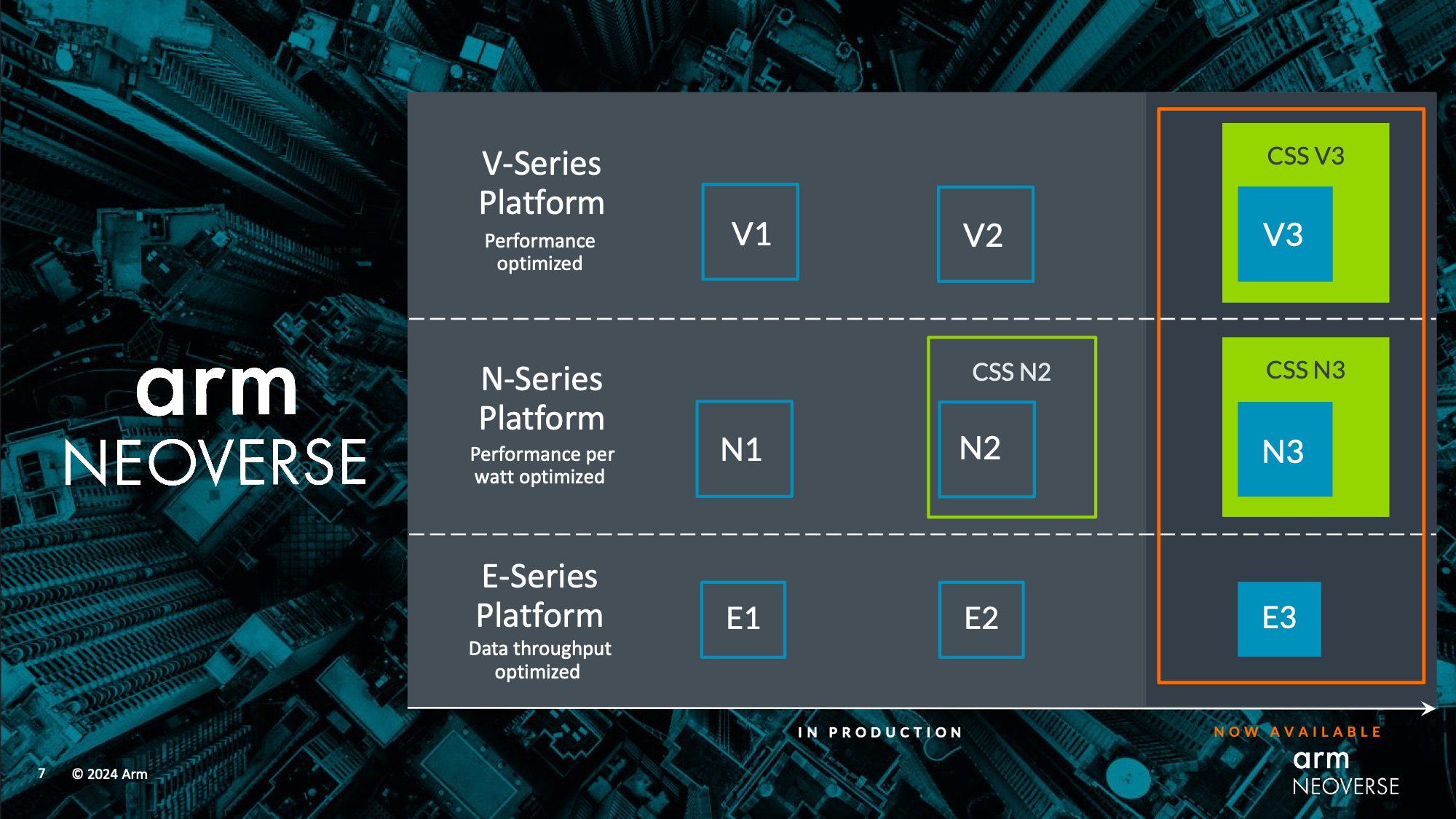

Hace poco más de 5 años, Arm anunció su iniciativa Neoverse para núcleos de CPU de servidor, nube e infraestructura. Redoblando sus esfuerzos para ingresar a lo grande en el mercado de CPU de infraestructura, la compañía emprendió un ambicioso plan plurianual para desarrollar lo que se convertiría en un trío de líneas de núcleos de CPU para abordar diferentes segmentos del mercado, que van desde potente serie V al pequeño núcleo de la serie E. Y aunque las cosas han ido un poco diferente de lo que Arm proyectó inicialmente, no están en condiciones de quejarse, ya que la línea Neoverse de núcleos de CPU nunca ha tenido tanto éxito como lo es ahora. Los diseños de CPU personalizados basados en núcleos Neoverse están de moda entre los proveedores de nube, y el mercado de infraestructura en general ha experimentado su propio aumento.

Ahora, mientras la empresa y sus clientes se dirigen hacia 2024 y un mercado informático que se encuentra en medio de otro cambio transformador debido a la demanda insaciable de hardware de IA, Arm se está preparando para lanzar su próxima generación de diseños de núcleos de CPU Neoverse a sus clientes. Y en el proceso, la compañía está alcanzando la culminación de la hoja de ruta original de Neoverse.

Esta mañana, la compañía está desvelando la arquitectura de CPU V3 (nombre en clave Poseidon) para sistemas de alto rendimiento, así como la arquitectura de CPU N3 (nombre en clave Hermes) para sistemas equilibrados. Estos diseños ahora están listos para que los clientes comiencen a integrarlos en sus propios diseños de chips, tanto con los diseños de núcleos de CPU individuales como con los subsistemas de cómputo (CSS) más grandes disponibles. Entre las diversas combinaciones de configuraciones de IP, Arm busca ofrecer algo para todos, y especialmente para los diseñadores de chips que buscan integrar IP ya preparadas para acelerar el desarrollo de sus propios chips.

Dicho esto, cabe señalar que el anuncio de hoy también es más ligero de lo que esperábamos de anuncios anteriores de Neoverse. Arm no publica ninguno de los detalles arquitectónicos profundos de las nuevas plataformas Neoverse hoy, por lo que si bien tenemos detalles de alto nivel sobre el hardware y algunas estimaciones básicas de rendimiento, los detalles subyacentes sobre los núcleos de la CPU y sus tuberías relacionadas son algo que Arm se está guardando para sí mismo hasta más tarde.

Neoverse V3: hasta 128 núcleos, con CXL 3.0 y HBM3, además de un diseño CSS

Comenzando con la arquitectura de alta gama de la plataforma Neoverse, el núcleo de CPU V3. Anteriormente incluido en las hojas de ruta de Arm como «V-Next» y bajo su nombre clave de Poseidon, Neoverse V3 es el diseño de arquitectura final en la hoja de ruta original de Neoverse de Arm, con Arm listo para finalmente cumplir con lo que imaginaron hace tanto tiempo.

Los núcleos Neoverse V se derivan tradicionalmente de diseños Cortex-X, y aunque Arm no revela ese nivel de detalle hoy, no hay razón para creer que eso haya cambiado. Sospecho que estamos ante un diseño de núcleo de CPU que se basa en gran medida en Cortex-X5, el diseño Cortex-X de próxima generación de Arm, en línea con el uso de X1 y X3 para V1 y V2 respectivamente. Pero esto es ciertamente una presunción por mi parte.

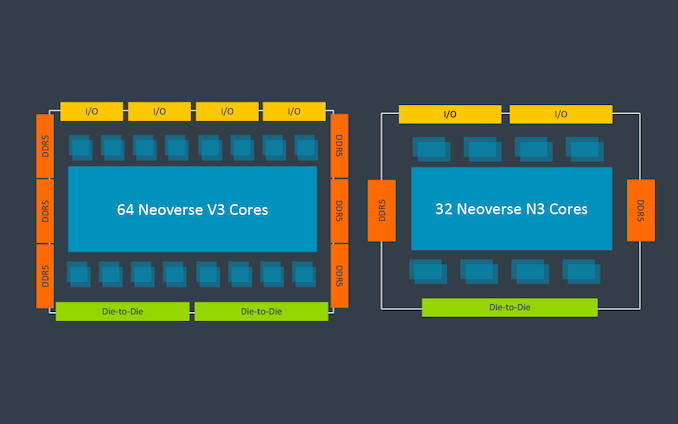

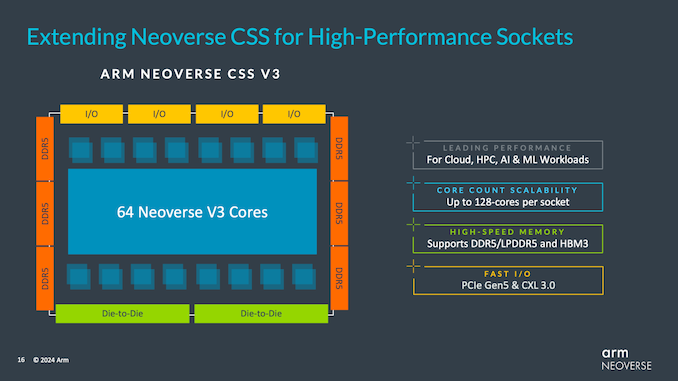

De todos modos, al igual que los núcleos de CPU de la serie V anteriores, el V3 está dirigido a las aplicaciones de mayor rendimiento y ofrece el rendimiento de un solo subproceso más alto de cualquier núcleo de CPU Arm Neoverse. Y con hasta 64 núcleos en un solo troquel (y dos troqueles/128 núcleos en un solo zócalo), V3 está destinado a competir en la gama alta tal como lo hizo V2 antes.

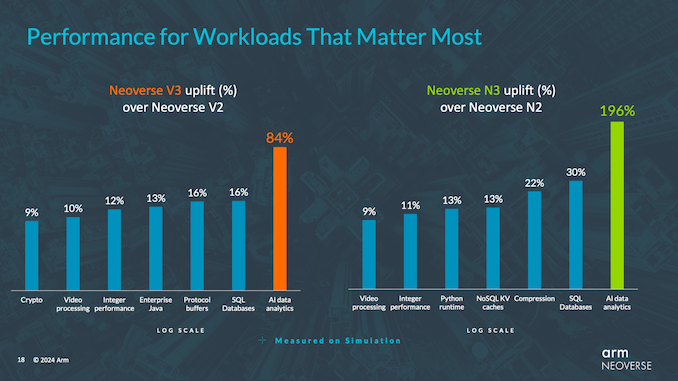

Arm no ha proporcionado una estimación de rendimiento generalizada para el núcleo de la CPU, pero en las simulaciones ven entre el 10% y el 20% para la mayoría de las cargas de trabajo, salvo el caso extremo del análisis de datos de IA (énfasis en los «análisis» y no en el «AI»). Volviendo a las primeras hojas de ruta de Arm, esto es inferior a las mejoras del 30% de generación en generación que buscaban inicialmente, pero, de nuevo, el V2 ni siquiera estaba en esas hojas de ruta en ese momento, por lo que los pasos de Arm se han vuelto más pequeños y un un poco más frecuente.

Nuevamente, aquí no tenemos detalles arquitectónicos detallados, pero sí tenemos algunos detalles de alto nivel de los cambios que vienen con la versión 3. Arm ha centrado gran parte de sus esfuerzos en el tejido de malla en múltiples puntos, por ejemplo. El propio V3 ha mejorado la forma en que se conecta a la tela de malla de Arm para aliviar la presión allí. Y la tela de malla en sí es nueva y reemplaza el probado CMN-700 de Arm con el nuevo CMN-S3, aunque no tenemos más detalles sobre lo que implica este último.

De lo contrario, V3 y su contraparte CSS vendrán con soporte para todos los formatos de memoria y E/S más recientes. Con E/S, la compatibilidad con CXL ha aumentado de CXL 2.0 a CXL3.0 – todavía sentado sobre PCIe 5.0. Mientras tanto, en el frente de la memoria, LPDDR5, DDR5 y HBM3 son compatibles con la IP de Arm.

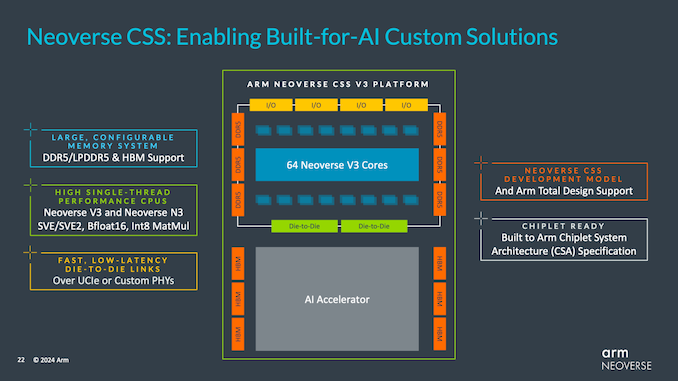

Y por primera vez para un núcleo de CPU de la serie V, Arm ofrece una versión CSS lista para usar de esta IP para una rápida integración en los diseños de chips de los clientes. Aunque la iniciativa CSS en sí es todavía bastante nueva, Arm dice que la estrategia ha demostrado ser muy exitosa, con proveedores de servicios en la nube bien financiados y hambrientos como Microsoft (Cobalt 100) que la adoptaron rápidamente para poder armar y desarrollar rápidamente sus propios diseños de chips. hardware puesto en servicio. Por lo tanto, Arm busca brindar el mismo nivel de simplicidad a los clientes de alto rendimiento, especialmente aquellos que solo necesitan un bloque IP de CPU probado para combinar con sus diseños de acelerador personalizados; Arm incluso proporciona un conjunto listo de conexiones de matriz a matriz. para agilizar aún más el proceso.

Y aunque esto se anunció técnicamente a principios de este mes, el diseño V3 CSS va de la mano con los esfuerzos de Arm para establecer su propio ecosistema de chiplets, Arm Chiplet System Architecture (CSA). La iniciativa CSA tiene como objetivo permitir a los clientes mezclar y combinar más fácilmente chiplets en sus productos, y CSA va más allá de la compatibilidad de protocolos y aborda aspectos como la gestión del sistema, DMA, seguridad y compatibilidad de software.

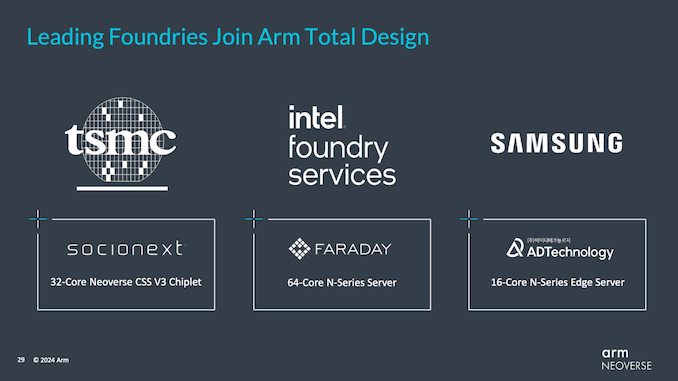

Finalmente, subrayando los rápidos tiempos de respuesta que Arm está imaginando con el IP CSS V3, la compañía ya está anunciando una victoria en el diseño con Socionext, quien está diseñando un chiplet CSS V3 de 32 núcleos que se fabricará en TSMC.

Arm Neoverse N3: 20% mejor rendimiento por vatio, para hasta 32 núcleos

La otra mitad del anuncio de IP de Neoverse de hoy es Neoverse N3 (nombre en clave Hermes), el último de la línea Arm de núcleos de CPU equilibrados y energéticamente eficientes para una amplia variedad de mercados.

Esta vez, con un enfoque aún mayor en su IP CSS, el diseño CSS N3 admite una variedad de núcleos de CPU, desde 8 hasta 32. En el caso de este último, Arm dice que su diseño puede operar con un TDP tan bajo como 40W. o un poco más de 1 vatio por núcleo de CPU, aunque la compañía no revela de qué nodo de proceso se trata.

En total, Arm promociona una mejora promedio del rendimiento por vatio del 20% para el N3 CSS sobre el N2 CSS. Las mejoras generales en el rendimiento suelen oscilar entre el 10% y el 30%, según la carga de trabajo específica.

Al igual que V3, Arm no ofrece muchos detalles arquitectónicos aquí. Pero dado que los diseños de la serie N históricamente comparten una gran cantidad de elementos de diseño con la serie Cortex-A7xx, no me sorprenderá descubrir que sucede lo mismo con el N3.

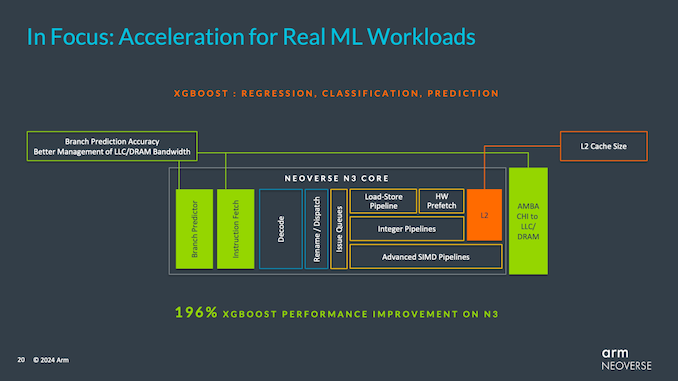

Mientras tanto, Arm ofrece un breve vistazo bajo el capó de N3 CSS para explicar su gran salto de rendimiento en el análisis de datos de IA, que se basa en la biblioteca XGBoost.

Para empezar, el tamaño de la caché L2 para N3 CSS ahora es de 2 MB por núcleo, frente a 1 MB para N2. De hecho, Arm también ha dedicado bastante esfuerzo a su subsistema general de caché y memoria, incluido el hecho de realizar algunos ajustes no revelados en su interfaz de host coherente para administrar mejor el tráfico y el ancho de banda de la memoria entre los núcleos de la CPU y el caché de último nivel (y más allá). . Aunque no está claro si N3 también está usando la nueva malla CMN-S3 de Arm, o si está limitada al V3. Mientras tanto, en la parte frontal del N3, el núcleo de la CPU presenta una unidad de predicción de ramas aún más precisa.

En conjunto, estas mejoras y más le están dando a Arm una mejora del 196% en el rendimiento de XGBoost y, de manera similar, la mejora de rendimiento del 84% que ve el núcleo de la CPU V3 en la misma carga de trabajo. Esto hace que el análisis de datos/XGBoost sea un caso atípico extremo en general, pero demuestra dónde ha puesto Arm algunos de sus esfuerzos con esta próxima generación de arquitecturas de CPU.

Aparte de esas mejoras principales, N3 también presenta muchas de las mejoras de E/S y memoria que también obtiene V3. Arm no ha proporcionado una lista detallada, pero nos dicen que es compatible con los últimos estándares PCIe y CXL, presumiblemente PCIe 5.0 y CXL 3.0, respectivamente. En particular, la hoja de ruta anterior de Arm tenía esta generación de hardware vinculada para admitir PCIe 6.0, pero como eso no llegó a la V3, parece que Arm tuvo que dar un paso atrás.

Finalmente, al igual que el CSS V3, el CSS N3 también presenta una interconexión de matriz a matriz. Aunque, como ocurre con la mayoría de los otros aspectos del hardware de la serie N, esto se ha reducido a una única interconexión. Por lo tanto, los proveedores de chips pueden optar por integrar N3 directamente en sus diseños de troqueles o conectarlo a un chiplet acelerador externo.

Una mirada hacia el futuro: Adonis, Dionisio y Lycius

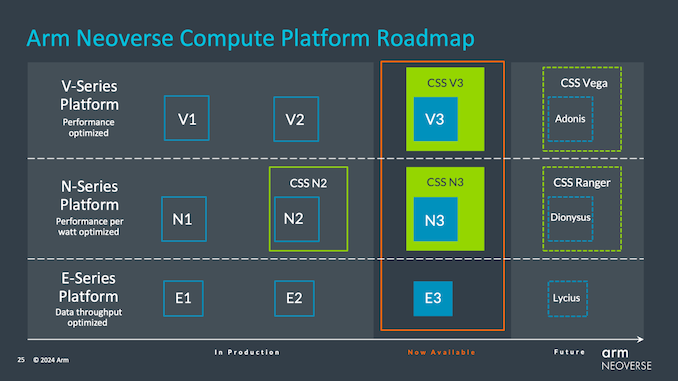

Finalmente, cuando Arm llegó al final de su hoja de ruta actual de Neoverse, la compañía proporciona una hoja de ruta para futuros lanzamientos de núcleos de CPU.

Cabe destacar que aquí se trata de una hoja de ruta menos detallada que la de Arm. Hoja de ruta de la era V2/N2, que incluía algunas notas de alto nivel sobre las tecnologías que se esperaba que estuvieran presentes. En cambio, esta hoja de ruta proporciona nombres en clave y poco más.

Al confirmar que Arm está trabajando en versiones de cuarta generación de los núcleos de CPU E, N y V, tenemos varios nombres en clave nuevos en general. Lycius será el próximo núcleo de la serie E de Neoverse (¿E4?), mientras que Dionysus será el próximo núcleo de la serie N y Adonis es el próximo núcleo de la serie V. Mientras tanto, sus respectivos subsistemas informáticos también están recibiendo nombres en clave, con CSS Ranger y CSS Vega para el CSS de la serie N y el CSS de la serie V, respectivamente.

En este momento, Arm no proporciona ninguna orientación sobre cuándo estarán listos estos diseños para sus clientes. Pero con V3/N3 IP recién saliendo a la venta para los clientes, es probable que la IP Neoverse de cuarta generación esté dentro de un par de años.