Con la llegada de la primavera llegan las lluvias, las flores y, en la industria tecnológica, la serie anual de simposios tecnológicos de TSMC. Con clientes repartidos por todo el mundo, la fundición taiwanesa ha adoptado una estrategia interesante para actualizar a sus clientes sobre sus fabulosos planes, organizando una serie de simposios desde Silicon Valley hasta Shanghai. El inicio de la serie cada año, y nos brinda nuestra primera mirada real a los planes de fundición actualizados de TSMC para los próximos años, es la parada de Santa Clara, donde ayer la compañía detalló varias tecnologías nuevas, que van desde procesos de litografía más avanzados hasta obleas masivas. -Opciones de embalaje de chips a escala.

Hoy publicamos varias historias basadas en las diferentes ofertas de TSMC, comenzando con el anuncio principal de TSMC: su nodo de proceso A16. Mientras tanto, para conocer el resto de las historias de nuestro simposio, asegúrese de consultar la lectura relacionada a continuación y vuelva a consultarla para ver historias adicionales.

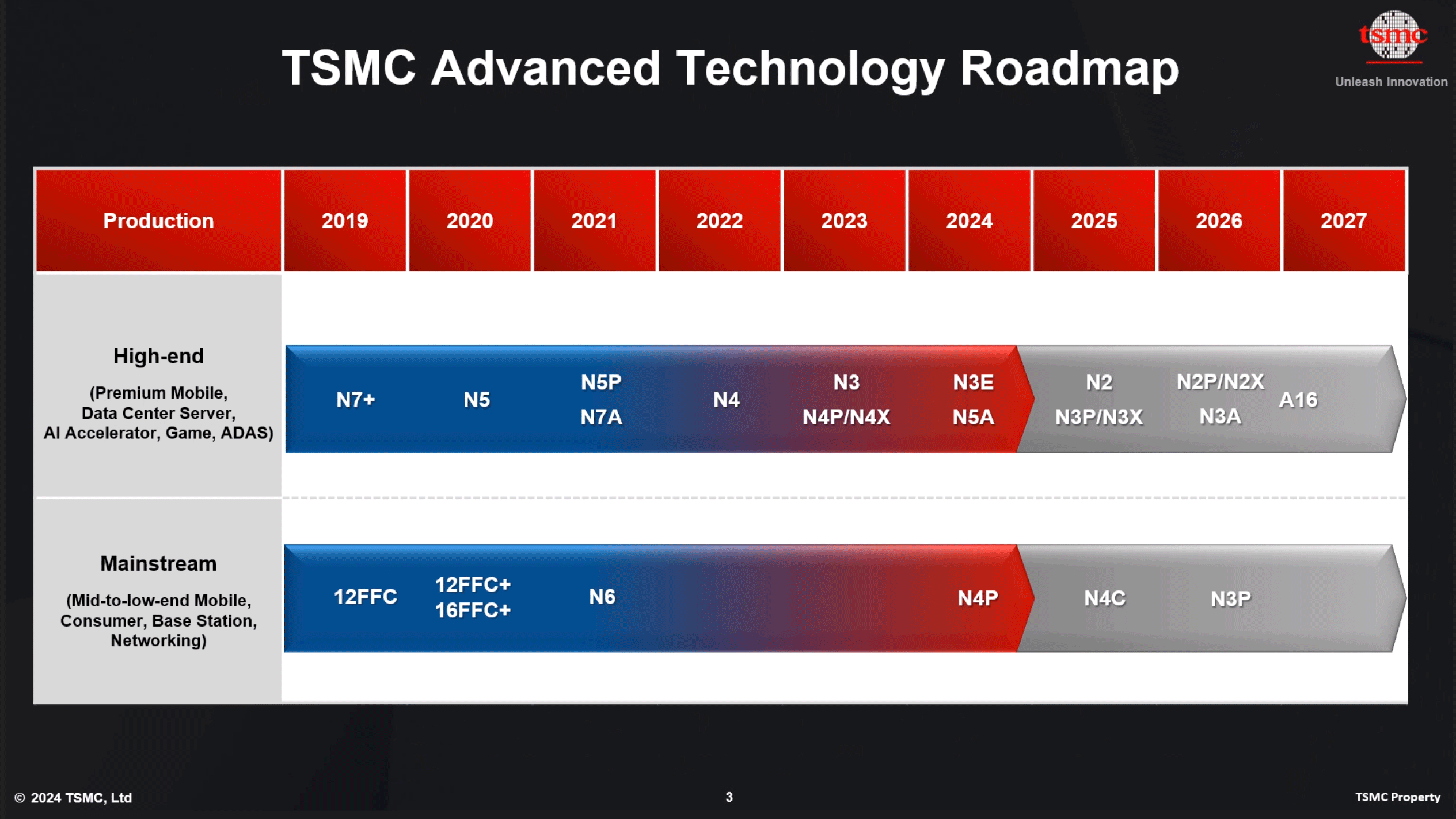

Encabezando su parada en Silicon Valley, TSMC anunció su primera tecnología de proceso ‘clase angstrom’: A16. Luego de un cambio en el cronograma de producción que eliminó la tecnología de red de suministro de energía trasera (BSPDN) del nodo N2P de TSMC, el nuevo nodo de producción de clase 1.6nm será ahora el primer proceso en introducir BSPDN en el repertorio de fabricación de chips de TSMC. Con la adición de capacidades de energía trasera y otras mejoras, TSMC espera que A16 ofrezca un rendimiento y eficiencia energética significativamente mejores en comparación con el proceso de fabricación N2P de TSMC. Estará disponible para los clientes de TSMC a partir del segundo semestre de 2026.

TSMC A16: Combinando GAAFET con entrega de energía trasera

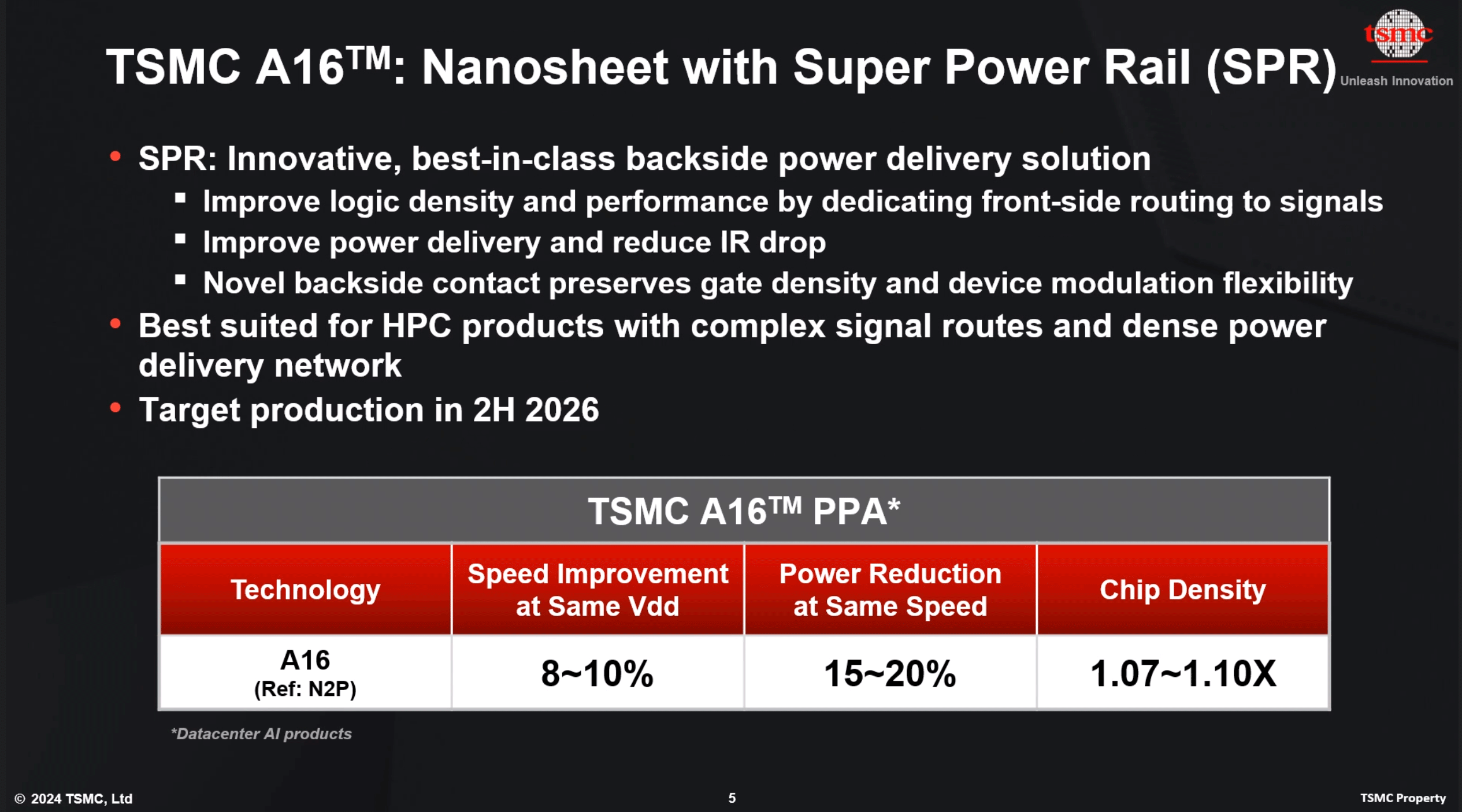

A un alto nivel, la tecnología de proceso A16 de TSMC se basará en transistores de nanohojas de puerta integral (GAAFET) y contará con un riel de alimentación en la parte trasera, que mejorará la entrega de energía y aumentará moderadamente la densidad del transistor. En comparación con el proceso de fabricación N2P de TSMC, se espera que A16 ofrezca una mejora de rendimiento del 8% al 10% con el mismo voltaje y complejidad, o una reducción del 15% al 20% en el consumo de energía con la misma frecuencia y número de transistores. TSMC no enumera parámetros de densidad detallados hasta ahora, pero la compañía dice que la densidad del chip aumentará de 1,07 a 1,10 veces, teniendo en cuenta que la densidad de los transistores depende en gran medida del tipo y las bibliotecas de transistores utilizados.

La innovación clave del nodo A16 de TSMC es su red de suministro de energía trasera Super Power Rail (SPR), una novedad para TSMC. El fabricante de chips contratado afirma que el SPR del A16 está diseñado específicamente para productos informáticos de alto rendimiento que presentan rutas de señal complejas y circuitos de potencia densos.

Como se señaló anteriormente, con el anuncio de esta semana, el A16 ahora se ha convertido en el vehículo de lanzamiento para la entrega de energía trasera en TSMC. la empresa estaba Inicialmente programado para ofrecer tecnología BSPDN con N2P en 2026, pero por razones que no están del todo claras, la tecnología fue eliminada de N2P y trasladada a A16. El calendario oficial de TSMC para N2P en 2023 siempre fue un poco flexible, por lo que es difícil decir si esto representa un retraso práctico para BSPDN en TSMC. Pero al mismo tiempo, es importante subrayar que A16 no solo cambiará su nombre a N2P, sino que será una tecnología distinta de N2P.

TSMC no es la única fábrica que busca la entrega de potencia trasera y, en consecuencia, estamos viendo surgir múltiples variaciones de la técnica en diferentes fábricas. La industria en general tiene tres enfoques para BSPDN: Buried Power Rail de Imec, PowerVia de Intel y ahora Super Power Rail de TSMC.

La técnica más antigua, Buried Power Rail de Imec, esencialmente coloca la red de suministro de energía en la parte posterior de la oblea y luego conecta el riel de energía de las celdas lógicas al contacto de energía mediante nano TSV. Esto permite cierta ampliación del área y no agrega demasiada complejidad a la producción. La segunda implementación, PowerVia de Intel, conecta la energía a la celda o al contacto del transistor, lo que proporciona un mejor resultado, pero a costa de complejidad.

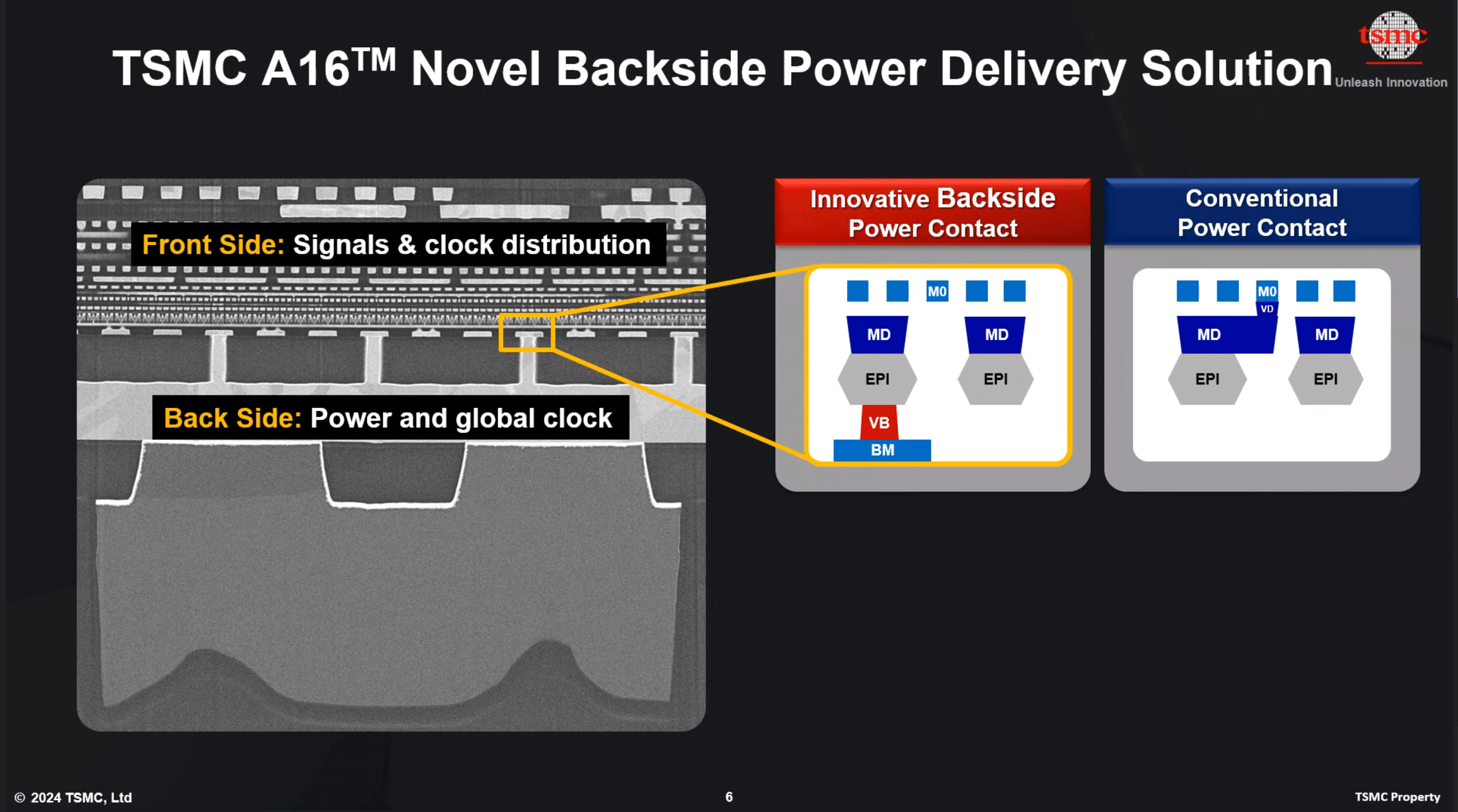

Finalmente, tenemos la nueva tecnología Super Power Rail BSPDN de TSMC, que conecta una red de alimentación trasera directamente a la fuente y al drenaje de cada transistor. Según TSMC, esta es la tecnología más eficiente en términos de escalamiento de área, pero la desventaja es que es la más compleja (y costosa) en términos de producción.

Que TSMC haya optado por la versión más compleja de BSPDN puede ser parte de la razón por la que la hemos visto eliminada de N2P, ya que implementarla en última instancia aumentará tanto el tiempo como los costos. Esto deja a A16 como el principal nodo de rendimiento de TSMC para el período 2026/2027, mientras que N2P puede posicionarse para ofrecer una combinación más equilibrada de rendimiento y rentabilidad.

La era Angstrom comienza a finales de 2026 con una nueva convención de nomenclatura de nodos

Finalmente, al igual que con Intel, también estamos viendo a TSMC adoptar una nueva convención de nomenclatura de nodos de proceso a partir de esta generación de tecnología. El nombre en sí es en gran medida arbitrario (y este ya ha sido el caso en la industria fabulosa desde hace varios años), pero como los nombres de los nodos actuales ya son de un solo dígito (por ejemplo, N2), la industria ha necesitado recalibrar los nombres de los nodos a algo más pequeño que el nanómetro. Y así hemos llegado a la ‘era angstrom’. Pero independientemente de cómo se llame exactamente o por qué se llama así, el punto importante es que A16 será el nodo de próxima generación más allá de los productos de clase de 2 nm de TSMC.

TSMC espera comenzar la producción en volumen del A16 en el segundo semestre de 2026, por lo que es probable que los primeros productos basados en esta tecnología lleguen al mercado en 2027. Dado el momento, es de suponer que el nodo de producción competirá contra Intel 14A; aunque con más de 2 años de antelación y sin nadie produciendo BSPDN en volumen hoy en día, todavía hay mucho tiempo para que cambien los planes y hojas de ruta.