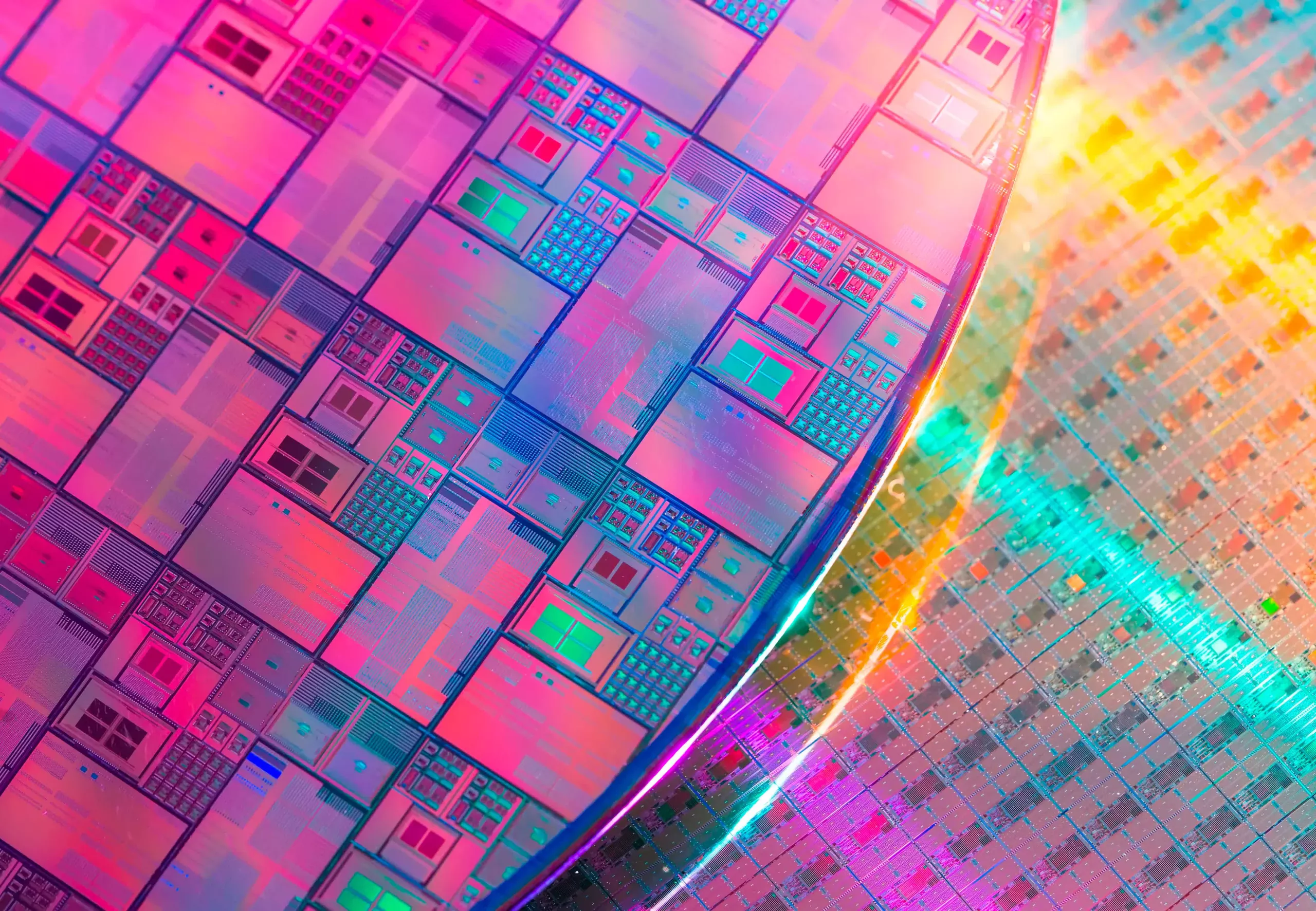

El panorama: La compañía global mostró cómo planea seguir aumentando la densidad de transistores durante los próximos años. También cree que la industria de los semiconductores también hará la transición a diseños basados en chiplets.

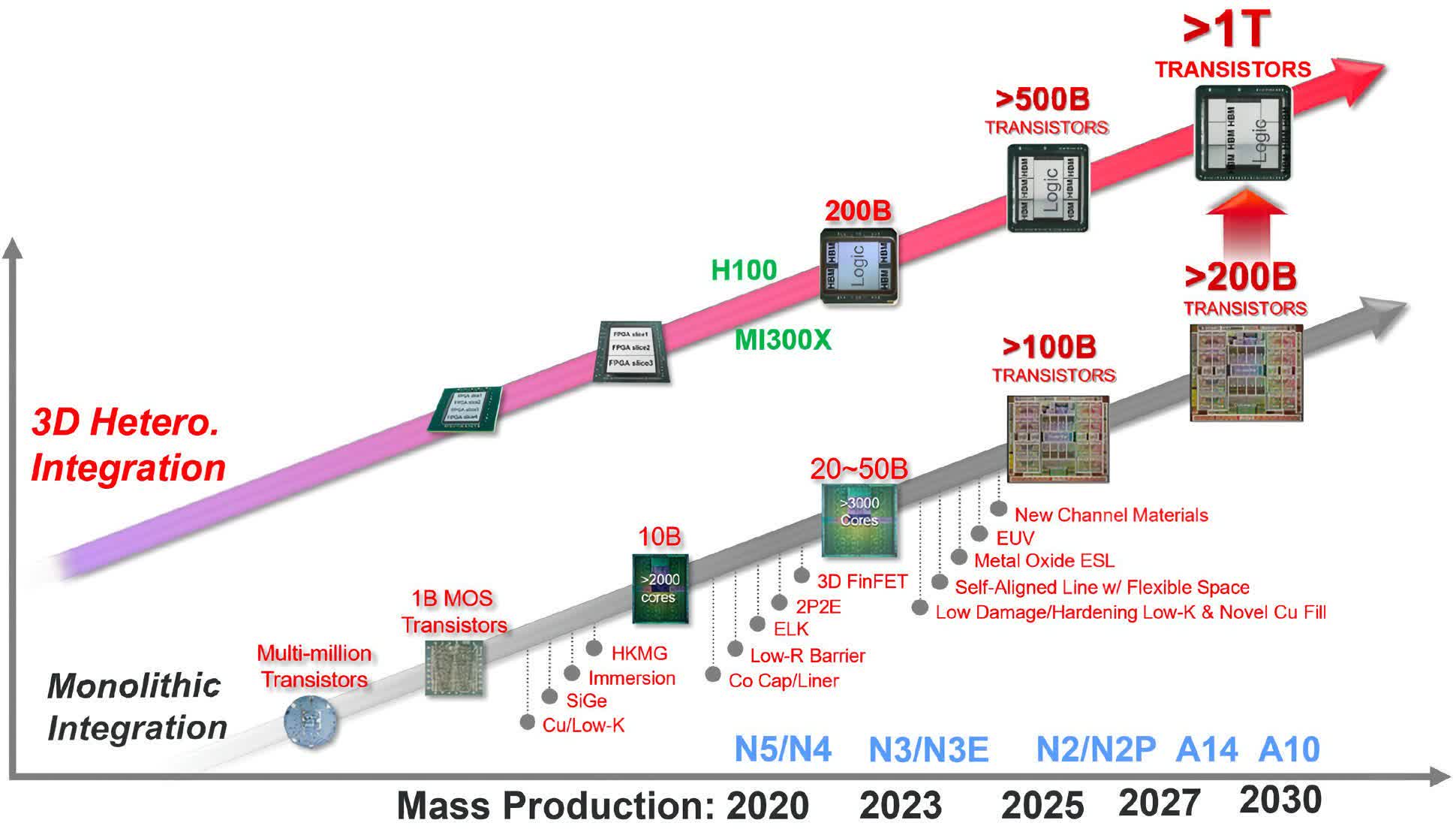

En el reciente conferencia IEDMTSMC reveló una hoja de ruta de productos para sus semiconductores y nodos de producción de próxima generación que culmina con la entrega de múltiples colecciones de diseños de chiplets apilados en 3D (3D Hetero Integration) con un billón de transistores en un paquete de un solo chip. Los avances en tecnologías de empaquetado, como CoWoS, InFO y SoIC, le permitirán alcanzar ese objetivo y para 2030 cree que sus diseños monolíticos podrían alcanzar los 200 mil millones de transistores.

El GH100 de 80 mil millones de transistores de Nvidia es uno de los procesadores monolíticos más sofisticados actualmente en el mercado. Sin embargo, a medida que el tamaño de estos procesadores siga creciendo y volviéndose más costosos, TSMC cree que los fabricantes adoptar arquitecturas multichiplet, como AMD lanzado recientemente Instinct MI300X y Ponte Vecchio de Intel, que tiene 100 mil millones de transistores.

Por ahora, TSMC continuará desarrollando nodos de producción N2 y N2P de clase 2 nm y procesos de fabricación A14 de clase 1,4 nm y A10 de 1 nm. La compañía espera comenzar la producción de 2 nm a fines de 2025. En 2028, pasará a un proceso A14 de 1,4 nm y, para 2030, espera producir transistores de 1 nm.

Mientras tanto, Intel está trabajando en su proceso de 2 nm (20A) y 1,8 nm (18A), que aproximadamente espera lanzamiento durante el mismo período de tiempo. Una ventaja de la nueva tecnología es la entrega de energía trasera, llamada PowerVia, que debería permitir para densidades lógicas más altas, velocidades de reloj de impulso más altas y menor fuga de energía, lo que resulta en diseños más eficientes energéticamente que podrían superar las ofertas de TSMC.

Como la fundición más grande del mundo, TSMC confía en que sus nodos de proceso superarán a cualquier producto de Intel. En una conferencia telefónica sobre resultados, el director ejecutivo de TSMC, CC Wei, dijo que una evaluación interna confirmado las mejoras de la tecnología N3P y que su nodo de fabricación de clase 3 nm demostró un «PPA comparable» al nodo 18A de Intel. Él espera que N3P sea aún mejor, con una «madurez tecnológica» más competitiva y significativas ventajas de costos.

Pat Gelsinger, director ejecutivo de Intel, que no ignora las palabras de lucha, afirmó que su nodo de proceso 18A superar Los chips de 2 nm de TSMC a pesar de su lanzamiento un año antes.

El mercado pronto podrá determinar cuál es mejor. El gigante de los chips con sede en Taiwán espera llevar N3P a la producción en masa en la segunda mitad de 2024, junto con sus productos 20A y 18A.