Si bien la mayor parte de la atención en TSMC se centra en sus nodos de vanguardia, como N3E y N2, se seguirán fabricando muchos chips utilizando tecnologías de proceso más maduras y probadas en los próximos años. Es por eso que TSMC ha seguido perfeccionando sus nodos existentes, incluidas sus ofertas de clase de 5 nm de generación actual. Con ese fin, en su Simposio de Tecnología de América del Norte 2024, la compañía presentó un nuevo nodo optimizado de clase 5 nm: N4C.

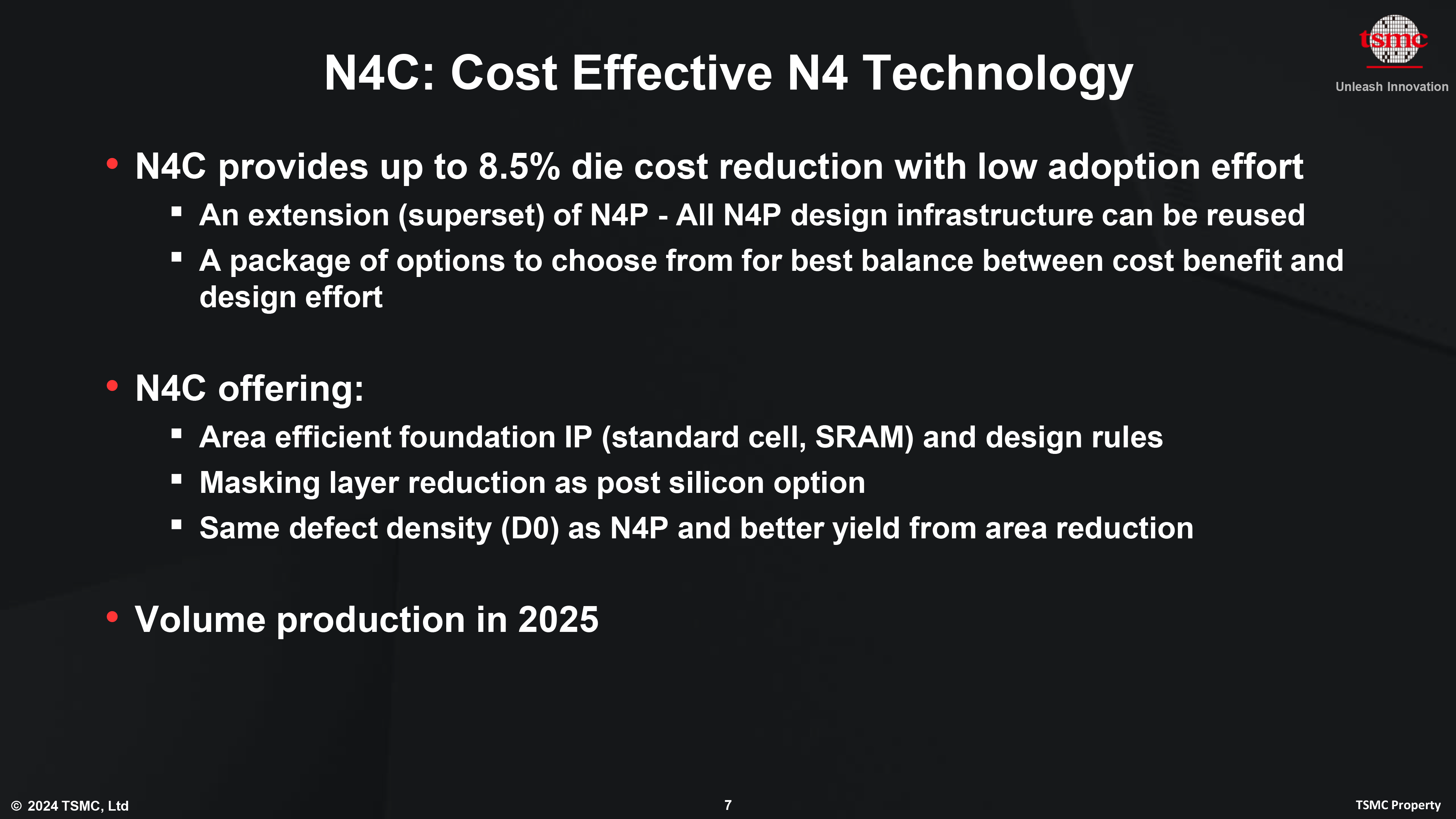

El proceso N4C de TSMC pertenece a la familia de nodos fabulosos de clase 5 nm de la compañía y es un superconjunto de N4P, la tecnología más avanzada de esa familia. En un intento por reducir aún más los costos de fabricación de 5 nm, TSMC está implementando varios cambios para N4C, incluida la remodelación de su celda estándar y su celda SRAM, cambiando algunas reglas de diseño y reduciendo la cantidad de capas de enmascaramiento. Como resultado de estas mejoras, la compañía espera que N4C logre tamaños de troqueles más pequeños y una reducción en la complejidad de la producción, lo que a su vez reducirá los costos de los troqueles hasta en un 8,5%. Además, con la misma tasa de densidad de defectos a nivel de oblea que N4P, N4C ofrece rendimientos funcionales aún mayores gracias a la reducción del área de su matriz.

«Entonces, no hemos terminado con nuestros 5 nm y 4 nm. [technologies]», dijo Kevin Zhang, vicepresidente de desarrollo comercial de TSMC. «De N5 a N4, hemos logrado una contracción óptica de mejora de la densidad del 4% y continuamos mejorando el rendimiento del transistor. Ahora incorporamos N4C a nuestra cartera de tecnología de 4 nm. N4C permite a nuestros clientes reducir sus costos al eliminar algunas de las máscaras y también mejorar el diseño IP original como una celda estándar y SRAM para reducir aún más el costo de propiedad general del producto».

TSMC dice que N4C puede usar la misma infraestructura de diseño que N4P, aunque no está claro si N5 y N4P IP pueden reutilizarse para chips basados en N4C. Mientras tanto, TSMC indica que ofrece varias opciones para que los fabricantes de chips encuentren el equilibrio adecuado entre costos, beneficios y esfuerzo de diseño, por lo que las empresas interesadas en adoptar tecnologías de proceso de clase 4 nm bien podrían adoptar N4C.

El desarrollo de N4C se produce cuando muchos de los clientes de diseño de chips de TSMC se están preparando para lanzar chips basados en la última generación de tecnología de proceso FinFET de la compañía, la serie N3 de 3 nm. Si bien se espera que N3 sea una familia exitosa, los altos costos de N3B han sido un problema, y la generación está marcada por una disminución del rendimiento y de la densidad de transistores en general. En consecuencia, N4C bien podría convertirse en un nodo importante y de larga duración en TSMC, y sería una buena opción para los clientes que desean apegarse a un nodo FinFET más rentable.

«Esta es una mejora muy significativa, estamos trabajando con nuestro cliente, básicamente para extraer más valor de su inversión en 4 nm», dijo Zhang.

TSMC espera comenzar la producción en volumen de chips N4C en algún momento del próximo año. Y dado que TSMC había producido la clase de 5 nm durante casi media década en ese momento, N4C debería poder comenzar a funcionar en términos de volumen y rendimiento.