En una palabra: TSMC se aventura en un territorio inexplorado con un enfoque novedoso para el empaquetado avanzado de chips. Según se informa, el fabricante de chips planea pasar de las obleas redondas convencionales a sustratos rectangulares, lo que permitirá colocar muchos más chips en cada oblea.

El propuesto El sustrato rectangular se encuentra actualmente en fase de pruebas. Con unas dimensiones sustanciales de 510 mm por 515 mm, supuestamente cuenta con más de tres veces el área utilizable de las obleas redondas actuales. Además, la forma rectangular reduce el desperdicio de espacio alrededor de los bordes. El estudio aún se encuentra en las primeras etapas y sus resultados pueden tardar algunos años en llegar al mercado.

Históricamente, los sustratos han sido redondos debido a sus ventajas de manipulación y resistencia superior. Sin embargo, el repentino interés en cambiar esta tendencia no es sorprendente dado el auge de la IA. Al igual que otros fabricantes de chips, TSMC está sintiendo la presión de la creciente demanda de potencia informática y pretende mantener el ritmo.

Es fascinante ver cómo el empaquetado de chips, alguna vez considerado el lado menos glamoroso de la fabricación de chips, se ha vuelto crucial para el avance de la tecnología de semiconductores.

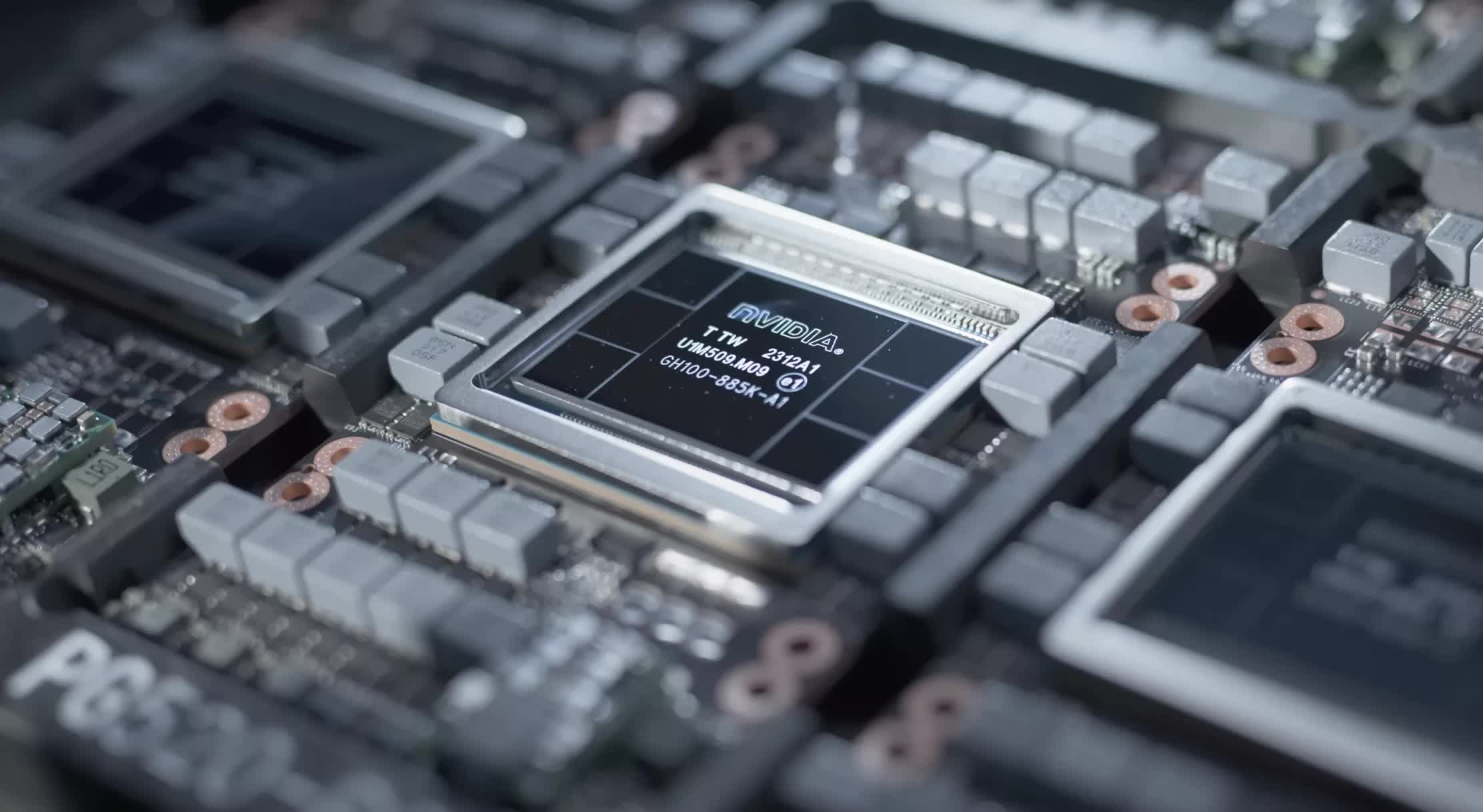

Por ejemplo, Nvidia H200 y B200 Los chips informáticos de IA se basan en la tecnología CoWoS (chip-on-wafer-on-sustrato) de última generación de TSMC. Este método de empaquetado avanzado combina múltiples unidades de procesamiento y memorias de gran ancho de banda, lo que da como resultado un rendimiento de datos más rápido y un rendimiento informático mejorado.

A medida que los chips crecen para acomodar más transistores y memoria, el actual estándar de oblea de 12 pulgadas podría no ser suficiente en un par de años. Ahí es donde entra en juego el experimento del sustrato rectangular de TSMC.

Sin embargo, este cambio no será un paseo por el parque. TSMC y sus proveedores deberán invertir mucho tiempo y recursos en el desarrollo. También tendrán que actualizar o reemplazar una cantidad sustancial de herramientas y materiales de producción. Un importante obstáculo es descubrir cómo aplicar fotorresistentes (materiales sensibles a la luz utilizados en la fabricación de chips) en estos nuevos sustratos rectangulares, dijo un ejecutivo de chips a Nikkei Asia.

TSMC no es el único fabricante que experimenta con tecnologías de sustratos de vanguardia. Su mayor competidor, SamsungSe rumorea que está invirtiendo mucho en investigación y desarrollo de sustratos de vidrio para la fabricación de chips, con el objetivo de lanzar productos al mercado ya en 2026. El uso de vidrio ofrece varias ventajas en comparación con los sustratos orgánicos, como una mayor planitud, que mejora la profundidad. de enfoque para procesos litográficos.