En una palabra: El ambicioso nodo 18A de Intel está lidiando con dos obstáculos importantes a medida que se acerca a la producción: tasas de rendimiento que languidecen por debajo del 10 por ciento y una desventaja crítica en la densidad de SRAM en comparación con el proceso N2 competidor de TSMC. Estos desafíos podrían impedir la implementación del nodo en las carteras de CPU, IA y chips personalizados de próxima generación de Intel.

Informes recientes indican que Intel enfrenta importantes desafíos de rendimiento con su nodo 18A, lo que podría retrasar su cronograma de producción en masa. Según el periódico surcoreano Chosun, la actual tasas de rendimiento están por debajo del 10 por ciento, lo que significa que casi nueve de cada 10 chips fabricados son defectuosos.

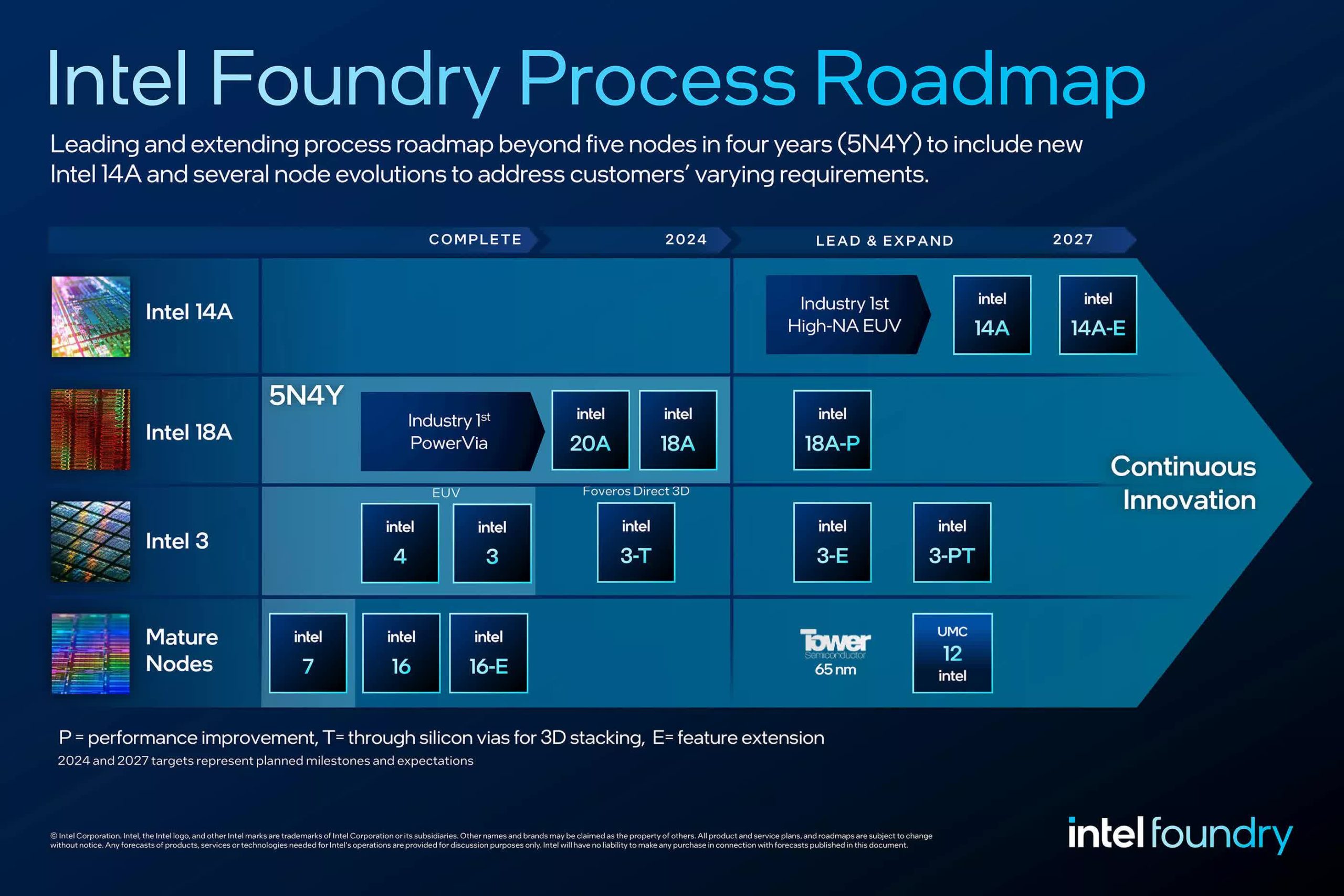

Este es un problema importante, particularmente porque Intel ya ha cancelado su nodo de proceso 20A (clase de 2 nm) para clientes de Foundry y transfirió recursos al nodo de 18A (clase de 1,8 nm). Si la tasa de rendimiento inferior al 10 por ciento resulta precisa, podría hacer que el nodo no sea apto para la producción comercial, al menos hasta que se realicen mejoras significativas.

El desafío de empaquetar transistores en diseños cada vez más densos en estos nodos de vanguardia es un obstáculo de ingeniería formidable. conmovedor toda la industria de los semiconductores. El rendimiento de la fundición de Samsung para procesos por debajo de 3 nm está actualmente por debajo del 50 por ciento, y se informa que el rendimiento de su tecnología Gate-All-Around (GAA) es tan bajo como del 10 al 20 por ciento.

Sin embargo, hay motivos para ser optimistas con respecto al nodo 18A de Intel, ya que la compañía todavía tiene varios meses para perfeccionar el proceso antes de su rampa de producción proyectada para 2025. La recompensa potencial es significativa, ya que 18A está previsto que alimente productos de alto perfil como los de Intel. Bosque de aguas claras chips de servidor, Lago Pantera CPU móviles y silicio de IA personalizado.

Si Intel puede mejorar rápidamente los rendimientos de 18A a niveles respetables (por encima del 60 por ciento en los próximos meses), aún se podría preparar el escenario para que este nodo impulse la próxima generación de productos de la empresa.

Dicho esto, los problemas de rendimiento no son el único desafío que enfrenta Intel con 18A. Según se informa, TSMC ha ganado ventaja en otra área crítica: la densidad de SRAM.

Según el Programa Avanzado ISSCC 2025, N2 de TSMC (clase de 2 nm) nodo se encoge celdas de bits SRAM de alta densidad de hasta aproximadamente 0,0175 μm², logrando una densidad de 38 Mb/mm². Por el contrario, el nodo 18A de Intel alcanza 0,021 μm² y 31,8Mb/mm², lo que se acerca más a los nodos N3E y N5 de la generación anterior de TSMC, una diferencia notable.

Dado que los diseños de chips exigen más SRAM, aumentar la densidad de estas pequeñas celdas de memoria es vital para mantener diseños compactos y eficientes. Aquí es donde entran en juego los transistores GAA (gate-all-around).

Al controlar el canal en todos los lados, los transistores GAA permiten un escalado más estricto en comparación con los finFET tradicionales. Este control estricto reduce las fugas en dimensiones pequeñas, lo que permite una SRAM de mayor densidad. Tanto Intel como TSMC están utilizando GAA para reducir sus celdas de bits SRAM, pero TSMC ha logrado empaquetarlas aún más densamente con su nodo N2.