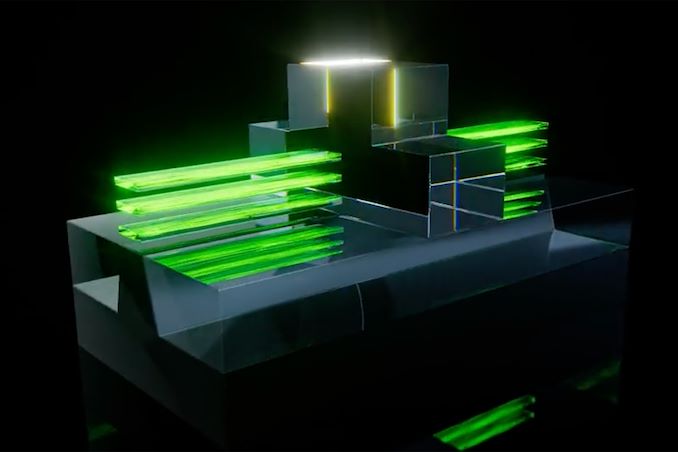

Además de revelar su hoja de ruta y planes relacionados con sus tecnologías de procesos de vanguardia actuales, TSMC también compartió el progreso de su N2 nodo como parte de su Simposios 2024. Según TSMC N2, el primer nodo de fabricación de clase de 2 nm de la compañía, que presenta predominantemente transistores de puerta integral, casi ha alcanzado sus objetivos de rendimiento y rendimiento, lo que la coloca en camino de ingresar a la fabricación de alto volumen en la segunda mitad de 2025. .

TSMC afirma que «el desarrollo de N2 va por buen camino y el de N2P es el siguiente». En particular, los dispositivos de nanohojas universales alcanzan actualmente más del 90% de su rendimiento esperado, mientras que los rendimientos de los dispositivos de 256 Mb SRAM (32 MB) ya superan el 80%, dependiendo del lote. Todo esto para un nodo que está a más de un año de la producción en masa.

Mientras tanto, el rendimiento promedio de una SRAM de 256 Mb fue de alrededor del 70 % en marzo de 2024, frente a alrededor del 35 % en abril de 2023. El rendimiento del dispositivo también ha mejorado al lograr frecuencias más altas manteniendo el consumo de energía bajo control.

El interés de los diseñadores de chips por la primera tecnología basada en transistores de nanohojas de clase 2 nm de TSMC también es significativo. El número de nuevas grabaciones (NTO) en el primer año de N2 es más del doble que en N5. Aunque dicho esto, dada la estrecha relación de trabajo de TSMC con un puñado de proveedores de gran volumen, sobre todo Appe, las NTO pueden ser una cifra muy engañosa, ya que el primer año de un nuevo nodo en TSMC tiene una capacidad limitada y, en consecuencia, la mayor parte de ese la capacidad va a los socios prioritarios de TSMC.

Mientras tanto, hubo considerablemente más grabaciones de N5 en su segundo año (algunas de ellas N5P, por supuesto) y N2 promete tener 2,6 veces más NTO en su segundo año. Así que el nodo parece bastante prometedor. De hecho, según las diapositivas de TSMC (que lamentablemente no podemos volver a publicar), N2 es más popular que N3 en términos de NTO tanto en el primer como en el segundo año de existencia.

En lo que respecta al segundo año de N2, en la segunda mitad de 2026 TSMC planea implementar su tecnología N2P, que promete beneficios adicionales de rendimiento y energía. Se espera que N2P mejore la frecuencia entre un 15% y un 20%, reduzca el consumo de energía entre un 30% y un 40% y aumente la densidad del chip en más de 1,15 veces en comparación con N3E, beneficios significativos al pasar a los nuevos transistores de nanohojas GAA.

Finalmente, para aquellas empresas que necesitan lo mejor en rendimiento, potencia y densidad, TSMC está preparada para ofrecer su Proceso A16 en 2026. ese nodo También traerá la entrega de energía trasera.lo que agregará costos, pero se espera que mejore en gran medida la eficiencia del rendimiento y el escalamiento.