Por qué es importante: Las empresas involucradas en el desarrollo de PCIe han estado diseñando conectores ópticos para el protocolo durante algún tiempo, pero en DevCon 2024 se vio un nuevo paso significativo hacia su uso en hardware del mundo real. La transición de CopperLink a óptico podría resultar crucial para los enormes aumentos de velocidad que se esperan de PCIe 6.0 y 7.0.

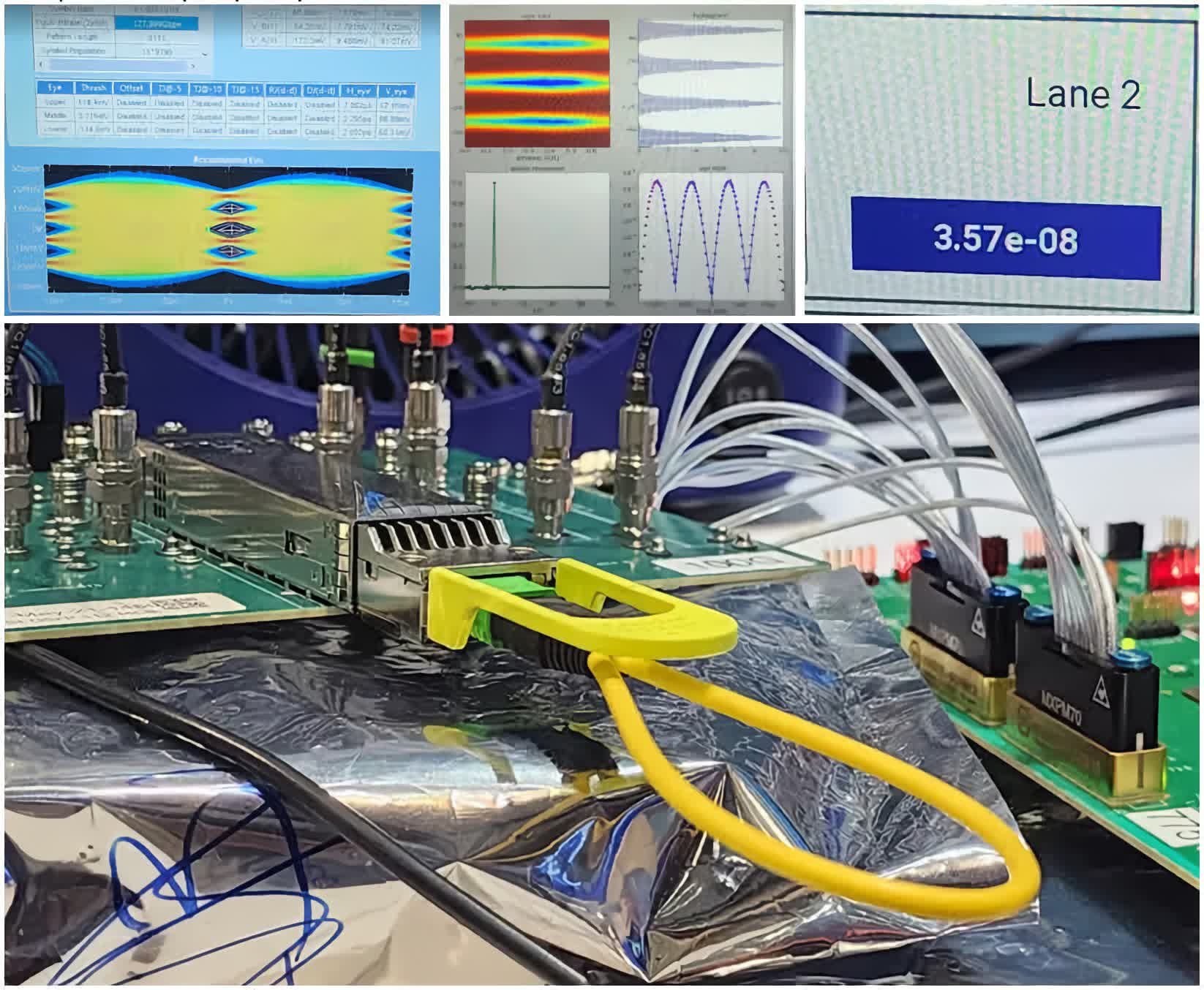

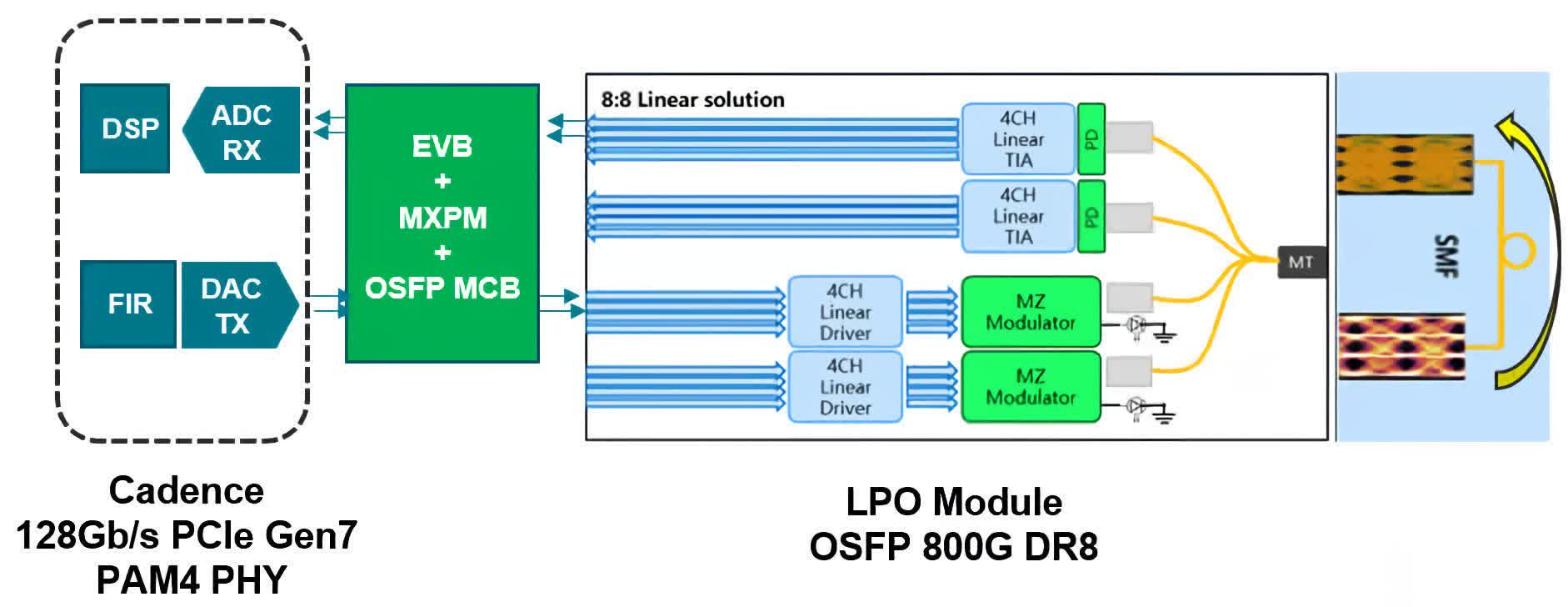

Cadence demostró una conexión PCIe 7.0 alcanzando 128 gigatransferencias por segundo (GT/s) utilizando piezas disponibles la semana pasada en PCI-SIG DevCon 2024. La prueba marca un importante paso adelante para las conexiones ópticas PCIe, el sucesor propuesto de CopperLink.

La demostración mantuvo la conexión continuamente durante más de dos días (durante toda la convención) sin interrupciones. Al mostrar las capacidades IX y RX de PCIe 7.0, Cadence mantuvo un BER previo a FEC de ~3E-8, lo que proporciona un amplio margen de RS FEC.

Los conectores PCIe ópticos están destinados a aplicaciones empresariales como hiperescala, computación en la nube, HPC y centros de datos. Como alternativa a CopperLink, podrían ofrecer a los constructores de servidores y centros de datos más opciones para una velocidad y ancho de banda superiores.

Especificaciones de Copper Link debutó en marzo y están diseñados para facilitar conexiones de 32 o 64 GT/s para PCIe 5.0 y 6.0, respectivamente. La tecnología óptica facilitará PCIe 6.0 y 7.0, pero los vertiginosos 128 GT/s que demostró Cadence sólo serán posibles con 7.0.

El grupo PCI-SIG estableció un equipo para explorar conexiones ópticas en agosto de 2023, y se planea una amplia gama de tecnologías para admitir PCIe, incluidos transceptores ópticos conectables, ópticas integradas, ópticas empaquetadas y E/S ópticas. Las especificaciones finales para mejorar el PCIe eléctrico mediante una solicitud de cambio de ingeniería están previstas para diciembre de 2024.

Las PC de consumo más modernas utilizan actualmente PCIe 5.0, sobre todo para impulsar velocidades de lectura de SSD superiores a 10 GB/s. PCI-SIG publicó las especificaciones completas para PCIe 6.0 a principios de 2022, y el estándar podría comenzar a surgir en el hardware empresarial a lo largo de 2024 y 2025.

Mientras tanto, las especificaciones preliminares de PCIe 7.0 se actualizaron a la versión 0.5 durante la DevCon la semana pasada, y se espera que las especificaciones finales lleguen el próximo año. El grupo PCI-SIG inicialmente tenía la intención de que el hardware del mundo real comenzara a aparecer en estado salvaje en 2027, pero empujado su proyección hasta 2028.

Las especificaciones PCIe 6.0 y 7.0 deberían admitir un ancho de banda de hasta 256 GB/s y 512 GB/s, respectivamente, en carriles x16. Sus innovaciones también incluyen modulación de amplitud de pulso con cuatro niveles (PAM4), corrección de errores directa ligera (FEC), verificación de redundancia cíclica (CRC) y unidades de control de flujo (Flits). Cadence demostró Flits y otras características nuevas para PCIe 6.0 en varios stands de DevCon.