JEDEC publicó el martes las especificaciones oficiales para GDDR7 DRAM, la última versión del estándar de memoria de larga data para tarjetas gráficas y otros dispositivos con GPU. La última generación de GDDR ofrece una combinación de capacidad de memoria y ganancias de ancho de banda de memoria, siendo este último impulsado principalmente por el cambio a señalización PAM3 en el bus de memoria. El último estándar de RAM para gráficos también aumenta la cantidad de canales por chip DRAM, agrega nuevos patrones de entrenamiento de interfaz e incorpora ECC integrado para mantener la confiabilidad efectiva de la memoria.

«JESD239 GDDR7 marca un avance sustancial en el diseño de memoria de alta velocidad», dijo Mian Quddus, presidente de la junta directiva de JEDEC. «Con el cambio a la señalización PAM3, la industria de la memoria tiene un nuevo camino para ampliar el rendimiento de los dispositivos GDDR e impulsar la evolución continua de los gráficos y diversas aplicaciones de alto rendimiento».

GDDR7 ha estado en desarrollo durante algunos años, y los miembros de JEDEC hicieron las primeras revelaciones sobre la tecnología de memoria hace aproximadamente un año, cuando Cadence reveló el uso de codificación PAM3 como parte de sus herramientas de validación. Desde entonces hemos tenido noticias de múltiple fabricantes de memoria que deberíamos esperar que la versión final de la memoria se lance en 2024, y el anuncio de JEDEC esencialmente llegará justo a tiempo.

Como se reveló anteriormente, el mayor cambio técnico con GDDR7 viene con el cambio de codificación de dos bits sin retorno a cero (NRZ) en el bus de memoria a Codificación de modulación de amplitud de pulso de tres bits (PAM3). Este cambio permite que GDDR7 transmita 3 bits en dos ciclos, un 50% más de datos que GDDR6 funcionando a una velocidad de reloj idéntica. Como resultado, GDDR7 puede admitir velocidades generales de transferencia de datos más altas, el componente crítico para hacer que cada generación de GDDR sea sucesivamente más rápida que su predecesora.

| Generaciones RDA | |||||

| GDDR7 | GDDR6X (No JEDEC) |

GDDR6 | |||

| B/N por pin | 32 Gbps (generación 1) 48 Gbps (especificación máxima) |

24 Gbps (Envío) | 24 Gbps (muestreo) | ||

| Densidad de viruta | 2GB (16GB) | 2GB (16GB) | 2GB (16GB) | ||

| Total en blanco y negro (bus de 256 bits) | 1024 GB/seg | 768 GB/seg | 768 GB/seg | ||

| Voltaje de RAM | 1,2 voltios | 1,35 voltios | 1,35 voltios | ||

| Velocidad de datos | RDA | RDA | RDA | ||

| Señalización | PAM-3 | PAM-4 | NRZ (binario) | ||

| Densidad máxima | 64GB | 32GB | 32GB | ||

| embalaje | 266 FBGA | 180FBGA | 180FBGA | ||

Se espera que la primera generación de GDDR7 funcione a velocidades de datos de alrededor de 32 Gbps por pin, y los fabricantes de memoria han hablado anteriormente de que velocidades de hasta 36 Gbps/pin son fácilmente alcanzables. Sin embargo, el estándar GDDR7 deja espacio para velocidades de datos aún más altas (hasta 48 Gbps/pin), y JEDEC llega incluso a promocionar chips de memoria GDDR7 que «alcanzan hasta 192 GB/s». [32b @ 48Gbps] por dispositivo» en su comunicado de prensa. En particular, se trata de un aumento significativamente mayor en el ancho de banda que lo que aporta la señalización PAM3 por sí sola, lo que significa que hay múltiples niveles de mejoras dentro del diseño de GDDR7.

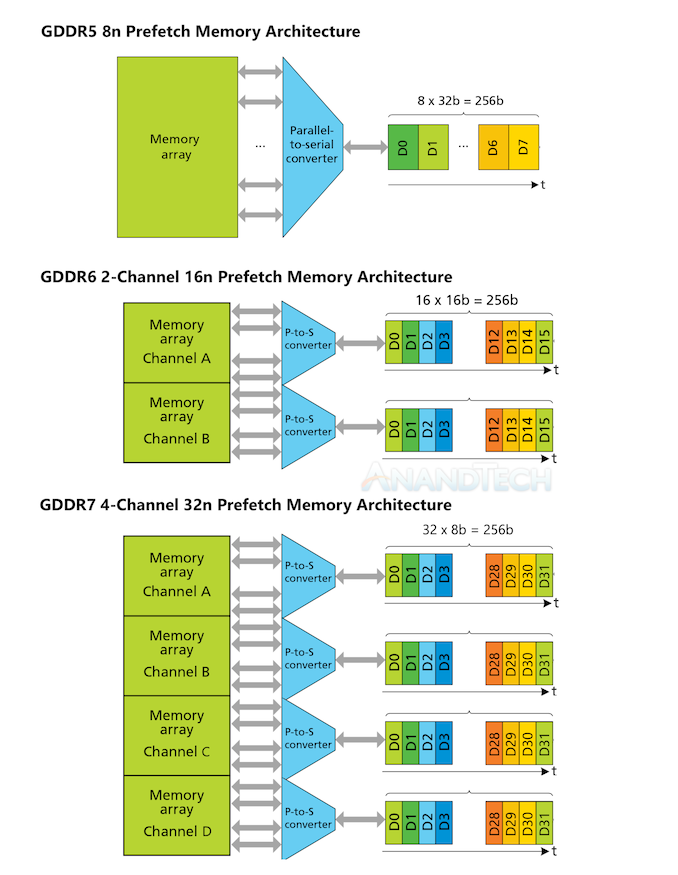

Profundizando en la especificación, JEDEC también ha subdividido una vez más un único chip de memoria GDDR de 32 bits en una mayor cantidad de canales. Mientras que GDDR6 ofrecía dos canales de 16 bits, GDDR7 lo amplía a cuatro canales de 8 bits. La distinción es algo arbitraria desde el punto de vista del usuario final (a pesar de todo, sigue siendo un chip de 32 bits que funciona a 32 Gbps/pin), pero tiene un gran impacto en cómo funciona internamente el chip. Especialmente porque JEDEC ha mantenido la captación previa de 256 bits por canal de GDDR5 y GDDR6, lo que convierte a GDDR7 en un diseño de captación previa de 32n.

Arquitectura del canal GDDR. Original Diagrama de la era GDDR6 Micron de cortesía

El impacto neto de todo esto es que, al reducir a la mitad el ancho del canal pero manteniendo el mismo tamaño de captación previa, JEDEC ha duplicado efectivamente la cantidad de datos que se captan previamente por ciclo de las celdas DRAM. Este es un truco bastante estándar para ampliar el ancho de banda de la memoria DRAM y es esencialmente lo mismo. JEDEC lo hizo con GDDR6 en 2018. Pero sirve como recordatorio de que las celdas DRAM siguen siendo muy lentas (del orden de cientos de MHz) y no se están volviendo más rápidas. Entonces, la única manera de alimentar buses de memoria más rápidos es recuperando cantidades cada vez mayores de datos de una sola vez.

El cambio en la cantidad de canales por chip de memoria también tiene un impacto menor en cómo funciona el modo «clamshell» multicanal para configuraciones de memoria de mayor capacidad. Mientras que GDDR6 accedió a un único canal de memoria desde cada chip en una configuración tipo clamshell, GDDR7 accederá a dos canales, lo que JEDEC llama modo de dos canales. Específicamente, este modo lee los canales A y C de cada chip. Es efectivamente idéntico a cómo se comporta el modo clamshell con GDDR6, y significa que si bien las configuraciones clamshell siguen siendo compatibles con esta última generación de memoria, no se emplean otros trucos para mejorar la capacidad de la memoria más allá de las densidades de chips de memoria cada vez mayores.

En ese sentido, el estándar GDDR7 agrega oficialmente soporte para dispositivos DRAM de 64 Gbit, el doble de la capacidad máxima de 32 Gbit de GDDR6/GDDR6X. También se siguen admitiendo capacidades sin potencia de dos, lo que permite chips de 24 Gbit y 48 Gbit. La compatibilidad con chips de memoria más grandes aumenta aún más la capacidad máxima de memoria de una tarjeta de video teórica de alta gama con un bus de memoria de 384 bits hasta 192 GB de memoria, un desarrollo que sin duda sería bien recibido por los operadores de centros de datos en la era de las grandes empresas. Modelos de IA del lenguaje. Dicho esto, sin embargo, todavía vemos regularmente chips de memoria de 16 Gbit utilizados en las tarjetas de memoria actuales, a pesar de que GDDR6 admite chips de 32 Gbit. Junto con el hecho de que Samsung y Micron ya han revelado que su primera generación de chips GDDR7 también alcanzará un máximo de 16 Gbit/24 Gbit respectivamente, es seguro decir que los chips de 64 Gbit están bastante lejos en el futuro en este momento (así que no vendan deshabilitado todavía sus tarjetas de 48 GB).

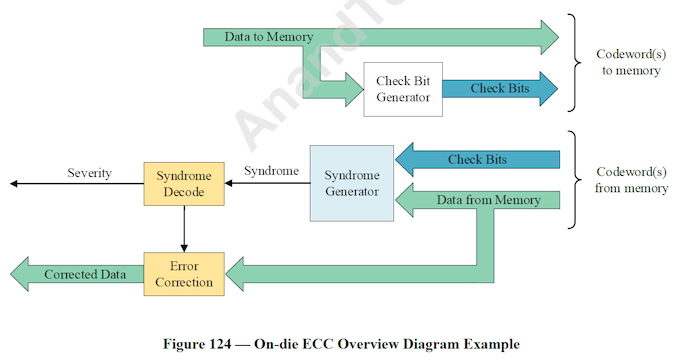

Para su última generación de tecnología de memoria, JEDEC también incluye varias características de confiabilidad de memoria nuevas para GDDR. En particular, las capacidades ECC integradas, similares a las que vimos con la introducción de DDR5. Y aunque no hemos podido obtener un comentario oficial de JEDEC sobre por qué optaron por incluir soporte ECC ahora, su inclusión no es sorprendente dados los requisitos de confiabilidad para DDR5. En resumen, a medida que ha aumentado la densidad de los chips de memoria, se ha vuelto cada vez más difícil producir una matriz «perfecta» sin fallas; por lo tanto, agregar ECC en el chip permite a los fabricantes de memoria mantener sus chips funcionando de manera confiable ante errores inevitables.

Esta figura se reproduce, con autorización, del documento JEDEC JESD239, figura 124.

Internamente, la especificación GDDR7 requiere un mínimo de 16 bits de datos de paridad por cada 256 bits de datos de usuario (6,25%), y JEDEC ofrece un ejemplo de implementación de un código de corrección de errores único (SEC) de 9 bits más una redundancia cíclica de 7 bits. cheque (CRC). En general, el ECC integrado GDDR7 debería poder corregir el 100 % de los errores de 1 bit y detectar el 100 % de los errores de 2 bits, cayendo al 99,3 % en el raro caso de errores de 3 bits. La información sobre errores de memoria también está disponible para el controlador de memoria, a través de lo que JEDEC denomina su protocolo de transparencia ECC integrado. Y aunque técnicamente está separado del propio ECC, GDDR7 también incluye otra característica de confiabilidad de la memoria con paridad de dirección de comando con bloqueo de comando (CAPARBLK), cuyo objetivo es mejorar la integridad del bus de dirección de comando.

De lo contrario, si bien no es probable que la inclusión de ECC en el chip tenga mayor impacto en las tarjetas de video de consumo que el que tuvo su inclusión para la memoria DDR5 y las plataformas de consumo allí, queda por ver qué significará esto para las estaciones de trabajo y los servidores. tarjetas de video. Los proveedores han utilizado ECC suave sobre memoria desprotegida durante varias generaciones; Es de suponer que este seguirá siendo el caso también para las tarjetas GDDR7, pero el uso regular de ECC suave hace que las cosas sean mucho más flexibles que en el espacio de la CPU.

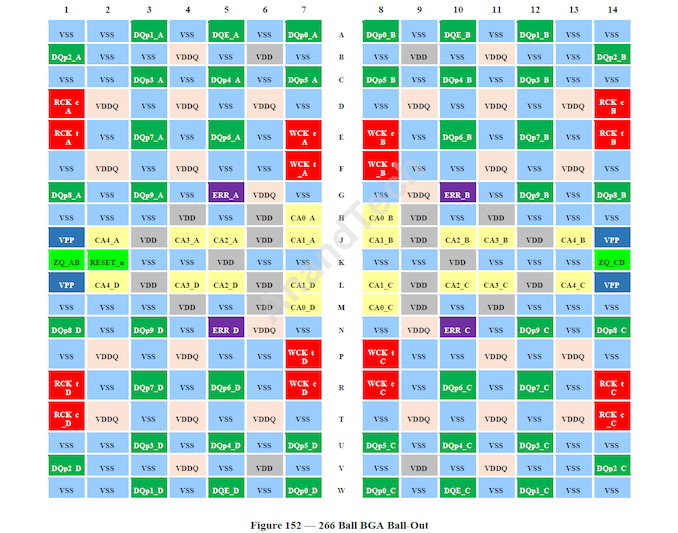

Esta figura se reproduce, con autorización, del documento JEDEC JESD239, figura 152.

Finalmente, GDDR7 también presenta un conjunto de otras características relacionadas con la confiabilidad, principalmente relacionadas con la ayuda al funcionamiento de PAM3. Esto incluye patrones de entrenamiento LFSR (registro de desplazamiento de retroalimentación lineal) independientes centrales con enmascaramiento ocular y contadores de errores. Los patrones de entrenamiento LFSR se utilizan para probar y ajustar la interfaz (para garantizar la eficiencia), el enmascaramiento ocular evalúa la calidad de la señal y los contadores de errores rastrean la cantidad de errores durante el entrenamiento.

Dejando a un lado las cuestiones técnicas, el anuncio de esta semana incluye declaraciones de apoyo de todos los jugadores habituales en ambos lados de la isla, incluidos AMD y NVIDA, y la trifecta Micron/Samsung/SKhynix. No hace falta decir que todas las partes están interesadas en utilizar o vender GDDR7 respectivamente, dadas las mejoras en capacidad de memoria y ancho de banda que traerá, y especialmente en esta era en la que cualquier cosa dirigida al mercado de la IA se vende como pan caliente.

No se anuncian productos específicos en este momento, pero como Samsung y Micron anunciaron previamente sus intenciones de enviar memoria GDDR7 este año, deberíamos ver nueva memoria (y nuevas GPU para combinarla) a finales de este año.

Los derechos de autor de los estándares y publicaciones de JEDEC pertenecen a la Asociación de Tecnología de Estado Sólido de JEDEC. Reservados todos los derechos.